výrobky Kategorie

- FM vysílač

- 0-50w 50w-1000w 2kw-10kw 10kw +

- televizní vysílač

- 0-50w 50-1kw 2kw-10kw

- FM anténa

- TV anténa

- anténa příslušenství

- Kabel konektor Power Splitter Dummy Load

- RF Transistor

- napájení

- audio Příslušenství

- DTV Front End Zařízení

- Link System

- STL systém Link systém Mikrovlnná trouba

- FM rádio

- Power Meter

- Ostatní produkty

- Speciální pro Coronavirus

Produkty Značky

Fmuser Sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikánština

- sq.fmuser.net -> albánština

- ar.fmuser.net -> arabština

- hy.fmuser.net -> Arménský

- az.fmuser.net -> Ázerbájdžánština

- eu.fmuser.net -> baskičtina

- be.fmuser.net -> běloruský

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> Katalánština

- zh-CN.fmuser.net -> čínština (zjednodušená)

- zh-TW.fmuser.net -> Čínsky (zjednodušeně)

- hr.fmuser.net -> chorvatština

- cs.fmuser.net -> čeština

- da.fmuser.net -> dánština

- nl.fmuser.net -> Dutch

- et.fmuser.net -> estonština

- tl.fmuser.net -> filipínský

- fi.fmuser.net -> finština

- fr.fmuser.net -> French

- gl.fmuser.net -> galicijština

- ka.fmuser.net -> gruzínština

- de.fmuser.net -> němčina

- el.fmuser.net -> Greek

- ht.fmuser.net -> haitská kreolština

- iw.fmuser.net -> hebrejština

- hi.fmuser.net -> hindština

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> islandština

- id.fmuser.net -> Indonéština

- ga.fmuser.net -> Irština

- it.fmuser.net -> Italian

- ja.fmuser.net -> japonština

- ko.fmuser.net -> korejština

- lv.fmuser.net -> lotyština

- lt.fmuser.net -> Litevština

- mk.fmuser.net -> makedonština

- ms.fmuser.net -> Malajština

- mt.fmuser.net -> maltština

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> perština

- pl.fmuser.net -> polština

- pt.fmuser.net -> portugalština

- ro.fmuser.net -> Rumunština

- ru.fmuser.net -> ruština

- sr.fmuser.net -> srbština

- sk.fmuser.net -> slovenština

- sl.fmuser.net -> Slovinština

- es.fmuser.net -> španělština

- sw.fmuser.net -> svahilština

- sv.fmuser.net -> švédština

- th.fmuser.net -> Thai

- tr.fmuser.net -> turečtina

- uk.fmuser.net -> ukrajinština

- ur.fmuser.net -> urdština

- vi.fmuser.net -> Vietnamská

- cy.fmuser.net -> velština

- yi.fmuser.net -> Jidiš

Co je Half Adder: Schéma obvodu a jeho aplikace

Date:2021/10/18 21:55:58 Hits:

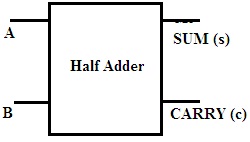

Half Adder je druh základního digitálního obvodu. Dříve se v analogových obvodech prováděly různé operace. Po objevení digitální elektroniky se v ní provádějí podobné operace. Digitální systémy jsou považovány za efektivní a spolehlivé. Mezi různými operacemi je jednou z nejvýznamnějších operací aritmetika. Zahrnuje sčítání, odčítání, násobení a dělení. Je však již známo, že to může být počítač, jakýkoli elektronický přístroj, jako je kalkulačka, může provádět matematické operace. Tyto operace se provádějí sestávají z binárních hodnot. To je možné díky přítomnosti určitých obvodů v něm. Tyto obvody se označují jako binární sčítačky a odčítače. Tento typ obvodů je určen pro binární kódy, kódy Excess-3 a další kódy. Další binární sčítačky jsou rozděleny do dvou typů. Jsou to: Poloviční sčítačka a Plná sčítačka Co je poloviční sčítačka? Digitální elektronický obvod, který slouží k provádění sčítání na binárních číslech, je definován jako poloviční sčítačka. Proces sčítání je denární, jediným rozdílem je zvolený číselný systém. V binárním systému číslování existuje pouze 0 a 1. Váha čísla je zcela založena na pozicích binárních číslic. Mezi těmi 1 a 0 je 1 považována za největší číslici a 0 za menší. Blokové schéma této sčítačky je Schéma poloviční sčítačky Poloviční sčítačka se skládá ze dvou vstupů a produkuje dva výstupy. Je považován za nejjednodušší digitální obvody. Vstupy do tohoto obvodu jsou bity, na kterých se má provádět sčítání. Získané výstupy jsou součet a přenos.

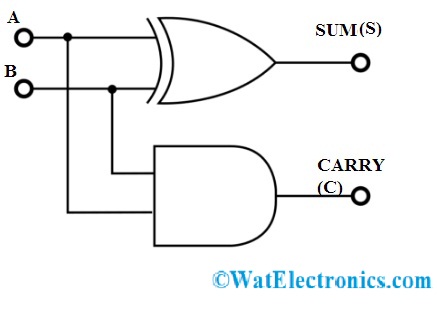

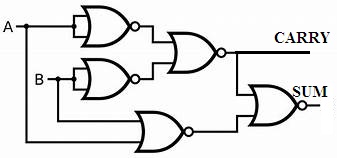

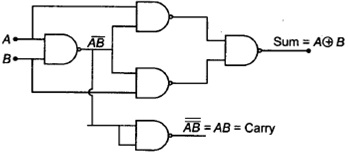

Schéma poloviční sčítačky Poloviční sčítačka se skládá ze dvou vstupů a produkuje dva výstupy. Je považován za nejjednodušší digitální obvody. Vstupy do tohoto obvodu jsou bity, na kterých se má provádět sčítání. Získané výstupy jsou součet a přenos.  Poloviční zmije Obvod této sčítačky se skládá ze dvou bran. Jsou to brány AND a XOR. Použité vstupy jsou stejné pro obě hradla přítomná v obvodu. Ale výstup se odebírá z každé brány. Výstup hradla XOR se označuje jako SUM a výstup AND je znám CARRY. Tabulka pravdy poloviční sčítačky Chcete-li získat vztah mezi získaným výstupem a aplikovaným vstupem, lze analyzovat pomocí tabulky známé jako tabulka pravdy.

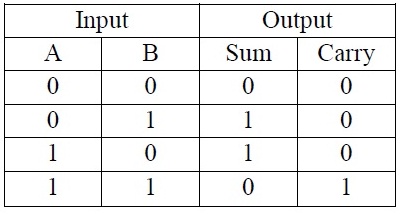

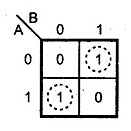

Poloviční zmije Obvod této sčítačky se skládá ze dvou bran. Jsou to brány AND a XOR. Použité vstupy jsou stejné pro obě hradla přítomná v obvodu. Ale výstup se odebírá z každé brány. Výstup hradla XOR se označuje jako SUM a výstup AND je znám CARRY. Tabulka pravdy poloviční sčítačky Chcete-li získat vztah mezi získaným výstupem a aplikovaným vstupem, lze analyzovat pomocí tabulky známé jako tabulka pravdy. Tabulka pravdivosti poloviční sčítačky Z výše uvedené pravdivostní tabulky jsou zřejmé následující body: Pokud A=0, B=0, to znamená, že oba použité vstupy jsou 0. Potom oba výstupy SUM a CARRY jsou 0. Mezi dvěma použitými vstupy, pokud někdo vstup je 1, pak SUM bude e1, ale CARRY je 0. Pokud jsou oba vstupy 1, pak se SUM bude rovnat 0 a CARRY se bude rovnat 1. Na základě použitých vstupů pokračuje poloviční sčítačka v operaci sčítání.RovniceRovnici pro tento typ obvodů lze realizovat pomocí konceptů součtu produktů (SOP) a produktů součtu (POS). Booleovská rovnice pro tento typ obvodů určuje vztah mezi aplikovanými vstupy a získanými výstupy. K určení rovnice jsou k-mapy nakresleny na základě hodnot pravdivostní tabulky. Skládá se ze dvou rovnic, protože jsou v něm použity dvě logická hradla. K-mapa přenosu je

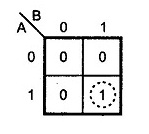

Tabulka pravdivosti poloviční sčítačky Z výše uvedené pravdivostní tabulky jsou zřejmé následující body: Pokud A=0, B=0, to znamená, že oba použité vstupy jsou 0. Potom oba výstupy SUM a CARRY jsou 0. Mezi dvěma použitými vstupy, pokud někdo vstup je 1, pak SUM bude e1, ale CARRY je 0. Pokud jsou oba vstupy 1, pak se SUM bude rovnat 0 a CARRY se bude rovnat 1. Na základě použitých vstupů pokračuje poloviční sčítačka v operaci sčítání.RovniceRovnici pro tento typ obvodů lze realizovat pomocí konceptů součtu produktů (SOP) a produktů součtu (POS). Booleovská rovnice pro tento typ obvodů určuje vztah mezi aplikovanými vstupy a získanými výstupy. K určení rovnice jsou k-mapy nakresleny na základě hodnot pravdivostní tabulky. Skládá se ze dvou rovnic, protože jsou v něm použity dvě logická hradla. K-mapa přenosu je  K-mapa AND bránaVýstupní rovnice CARRY se získá z brány AND.C=A.BBooleovský výraz pro SUM je realizován formou SOP. Proto K-mapa pro SUM je

K-mapa AND bránaVýstupní rovnice CARRY se získá z brány AND.C=A.BBooleovský výraz pro SUM je realizován formou SOP. Proto K-mapa pro SUM je K-mapa pro součet (XOR) Určená rovnice je S= A⊕ BAPoužitíAplikace této základní sčítačky jsou následující Pro provádění sčítání na binárních bitech aritmetická a logická jednotka přítomná v počítači preferuje tento sčítací obvod. Kombinace obvodů poloviční sčítačky vede k vytvoření obvodu Full Adder. Tyto logické obvody jsou upřednostňovány při návrhu kalkulaček. Pro výpočet adres a tabulek jsou upřednostňovány tyto obvody. Místo jediného přidání jsou tyto obvody schopné zvládat různé aplikace v digitálních obvodech. Dále se to stane srdcem digitální elektroniky. Kód VHDL Kód VHDL pro obvody Half Adder islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;data architektury poloviny_sčítačky isbeginsum<= a xor b;přenášejí <= a a b;koncová data;FAQs1. Co myslíte sčítačkou? Digitální obvody, jejichž jediným účelem je provádět sčítání, se nazývají sčítačky. Toto jsou hlavní součásti ALU. Sčítačky fungují navíc k různým formátům čísel. Výstupy sčítaček jsou sum a carry.2. Jaká jsou omezení poloviční sčítačky? Přenosový bit generovaný z předchozího bitu nelze přidat, je omezením tohoto sčítače. Pro provádění sčítání pro více bitů nelze tyto obvody upřednostňovat.3. Jak implementovat Half Adder pomocí NOR Gate? Implementaci tohoto typu adderu lze také provést pomocí NOR brány. Toto je další univerzální brána.

K-mapa pro součet (XOR) Určená rovnice je S= A⊕ BAPoužitíAplikace této základní sčítačky jsou následující Pro provádění sčítání na binárních bitech aritmetická a logická jednotka přítomná v počítači preferuje tento sčítací obvod. Kombinace obvodů poloviční sčítačky vede k vytvoření obvodu Full Adder. Tyto logické obvody jsou upřednostňovány při návrhu kalkulaček. Pro výpočet adres a tabulek jsou upřednostňovány tyto obvody. Místo jediného přidání jsou tyto obvody schopné zvládat různé aplikace v digitálních obvodech. Dále se to stane srdcem digitální elektroniky. Kód VHDL Kód VHDL pro obvody Half Adder islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;data architektury poloviny_sčítačky isbeginsum<= a xor b;přenášejí <= a a b;koncová data;FAQs1. Co myslíte sčítačkou? Digitální obvody, jejichž jediným účelem je provádět sčítání, se nazývají sčítačky. Toto jsou hlavní součásti ALU. Sčítačky fungují navíc k různým formátům čísel. Výstupy sčítaček jsou sum a carry.2. Jaká jsou omezení poloviční sčítačky? Přenosový bit generovaný z předchozího bitu nelze přidat, je omezením tohoto sčítače. Pro provádění sčítání pro více bitů nelze tyto obvody upřednostňovat.3. Jak implementovat Half Adder pomocí NOR Gate? Implementaci tohoto typu adderu lze také provést pomocí NOR brány. Toto je další univerzální brána. Half Adder using NOR gates4. Jak implementovat Half Adder pomocí brány NAND? Brána NAND je jedním z druhů univerzálních bran. Znamená to, že pomocí hradel NAND je možné navrhnout jakýkoli druh obvodu.

Half Adder using NOR gates4. Jak implementovat Half Adder pomocí brány NAND? Brána NAND je jedním z druhů univerzálních bran. Znamená to, že pomocí hradel NAND je možné navrhnout jakýkoli druh obvodu. Half Adder Z výše uvedeného obvodu lze přenosový výstup generovat přivedením výstupu jednoho hradla NAND na vstup jako druhého hradla NAND. To není nic jiného než známý výstup získaný z hradla AND. Výstupní rovnici SUM lze vygenerovat aplikací výstupu počátečního hradla NAND spolu s jednotlivými vstupy A a B na další hradla NAND. Nakonec jsou výstupy získané těmito branami NAND znovu použity na bránu. Proto je generován výstup pro SUM. Proto lze základní sčítačku v digitálním obvodu navrhnout pomocí různých logických hradel. Ale sčítání více bitů se komplikuje a považuje se za omezení poloviční sčítačky. Můžete popsat, který IC se používá pro inkrementální operaci v praktických čítačích?

Half Adder Z výše uvedeného obvodu lze přenosový výstup generovat přivedením výstupu jednoho hradla NAND na vstup jako druhého hradla NAND. To není nic jiného než známý výstup získaný z hradla AND. Výstupní rovnici SUM lze vygenerovat aplikací výstupu počátečního hradla NAND spolu s jednotlivými vstupy A a B na další hradla NAND. Nakonec jsou výstupy získané těmito branami NAND znovu použity na bránu. Proto je generován výstup pro SUM. Proto lze základní sčítačku v digitálním obvodu navrhnout pomocí různých logických hradel. Ale sčítání více bitů se komplikuje a považuje se za omezení poloviční sčítačky. Můžete popsat, který IC se používá pro inkrementální operaci v praktických čítačích?

Zanechat vzkaz

Seznam zpráv

Komentáře Loading ...